# **Multi-Feature, Synchronous** plus Auxiliary PWM **Controller**

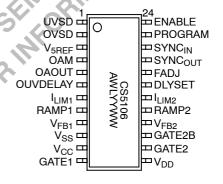

The CS5106 is a fixed frequency, current mode controller with one single NFET driver and one dual FET, synchronous driver. The synchronous driver allows for increased efficiency of the main isolated power stage and the single driver allows the designer to develop auxiliary supplies for controller power as well as secondary side house keeping. In addition, because the synchronous drivers have programmable FET non-overlap, the CS5106 is an ideal controller for soft-switched converter topologies.

The CS5106 is specifically designed for isolated topologies where speed, flexibility, reduced size and reduced component count are requirements. The controller contains the following features: Undervoltage Shutdown, Overvoltage Shutdown, Programmable Frequency, Programmable Synchronous Non-Overlap Time, Master/Slave Clocking with Frequency Range Detection, Enable, Output Undervoltage Protection with Timer, 20 mA 5.0 V Output, 80 ns PWM propagation delay, and Controlled Hiccup Mode.

The CS5106 has junction temperature and supply ranges of -40°C Inon-Overlap

Load

12 V Fixed Auxiliary Supply Control

Under and Overvoltage Shutdown

Output Undervoltage Protection with Timer

Master/Slave Clock Sync Capability

Sync Frequency Range Detection

80 ns PWM Propagation Delay

20 mA 5.0 V Reference Output

Small 24 Lead SSOP Package

Controlled Hiccup Mode to 125°C and 9.0 V to 16 V respectively and is available in the 24 lead

### ON Semiconductor™

http://onsemi.com

SSOP-24 SW SUFFIX CASE 940D

### PIN CONNECTIONS AND MARKING DIAGRAM

= Assembly Location

WL, L = Wafer Lot = Year = Work Week WW. W

#### **ORDERING INFORMATION**

| Device       | Package | Shipping         |

|--------------|---------|------------------|

| CS5106LSW24  | SSOP-24 | 59 Units/Rail    |

| CS5106LSWR24 | SSOP-24 | 2000 Tape & Reel |

1

Figure 1. Application Diagram, 48 V to 3.3 V Forward Converter with Synchronous Rectifiers

# **ABSOLUTE MAXIMUM RATINGS\***

| Rating                                         | Rating                             |             | Unit |

|------------------------------------------------|------------------------------------|-------------|------|

| Operating Junction Temperature, T <sub>J</sub> |                                    | 150         | °C   |

| Operating Temperature Range, T <sub>A</sub>    |                                    | -40 to 85   | °C   |

| Storage Temperature Range, T <sub>S</sub>      |                                    | -65 to +150 | °C   |

| ESD Susceptibility (Human Body Model)          |                                    | 2.0         | kV   |

| Lead Temperature Soldering:                    | Reflow: (SMD styles only) (Note 1) | 230 peak    | °C   |

<sup>1. 60</sup> second maximum above 183°C.

# **ABSOLUTE MAXIMUM RATINGS**

| Pin Name                                        | Pin Symbol          | V <sub>MAX</sub> | V <sub>MIN</sub> | I <sub>SOURCE</sub>   | I <sub>SINK</sub>     |

|-------------------------------------------------|---------------------|------------------|------------------|-----------------------|-----------------------|

| Undervoltage Shutdown Input                     | UVSD                | 6.0 V            | -0.3 V           | 1.0 mA                | N/A                   |

| Overvoltage Shutdown Input                      | OVSD                | 6.0 V            | -0.3 V           | 1.0 mA                | N/A                   |

| 5.0 V Reference Output                          | V <sub>5REF</sub>   | 6.0 V            | -0.3 V           | 150 mA                | 25 mA                 |

| Error Amp Minus Input                           | OAM                 | 6.0 V            | -0.3 V           | 250 μΑ                | 1.2 mA                |

| Error Amp Output                                | OAOUT               | 6.0 V            | -0.3 V           | 300 μΑ                | 100 mA                |

| Output Overcurrent Timer Capacitor              | OUVDELAY            | 6.0 V            | -0.3 V           | 15 μΑ                 | N/A                   |

| Auxiliary Primary Side Current<br>Limit Input   | I <sub>LIM1</sub>   | 6.0 V            | -0.3 V           | 10 μΑ                 | N/A                   |

| Auxiliary Primary Side Current<br>Ramp Input    | RAMP1               | 6.0 V            | -0.3 V           | 10 μΑ                 | N/A                   |

| Auxiliary Voltage Feedback Input                | V <sub>FB1</sub>    | 6.0 V            | -0.3 V           | 5.0 μΑ                | 100 μΑ                |

| Bootstrapped Power Input                        | V <sub>SS</sub>     | 20 V             | -0.3 V           | 2.0 μΑ                | 0.5 A Peak, 300 mA DC |

| Main Power Input                                | V <sub>CC</sub>     | 20 V             | -0.3 V           | See Note 2            | 0.5 A Peak, 300 mA DC |

| Auxiliary FET Driver Output                     | GATE1               | 20 V             | -0.3 V           | 0.5 A Peak, 100 mA DC | 0.5 A Peak, 100 mA DC |

| Ground                                          | GND                 | 0·V              | 0 V              | 0.5 A Peak            | N/A, 300 mA DC        |

| Synchronous FET Driver Output                   | GATE2               | 20 V             | -0.3 V           | 0.5 A Peak, 100 mA DC | 0.5 A Peak, 100 mA DC |

| Synchronous FET Driver Output B                 | GATE2B              | 20 V             | -0.3 V           | 0.5 A Peak, 100 mA DC | 0.5 A Peak, 100 mA DC |

| Synchronous Voltage Feedback<br>Input           | V <sub>FB2</sub>    | 6.0 V            | -0.3 V           | 10 μΑ                 | 100 μΑ                |

| Synchronous Primary Side Current<br>Ramp Input  | RAMP2               | 6.0 V            | -0.3 V           | 10 μΑ                 | N/A                   |

| Synchronous Primary Side Current<br>Limit Input | l <sub>LIM2</sub>   | 6.0 V            | -0.3 V           | 10 μΑ                 | N/A                   |

| Gate Non-Overlap Programming<br>Input           | DLYSET              | 2.5 V            | -0.3 V           | 125 μΑ                | N/A                   |

| Frequency Programming Input                     | FADJ                | 2.5 V            | -0.3 V           | 125 μΑ                | N/A                   |

| Clock Master Output                             | SYNC <sub>OUT</sub> | 6.0 V            | -0.3 V           | 50 mA                 | 100 mA                |

| Clock Slave Input                               | SYNC <sub>IN</sub>  | 6.0 V            | -0.3 V           | N/A                   | 1.0 mA                |

| Enable Programming Input                        | PROGRAM             | 16 V             | -0.3 V           | 30 μΑ                 | N/A                   |

| Enable Input                                    | ENABLE              | 16 V             | -0.3 V           | 300 μΑ                | N/A                   |

<sup>2.</sup> Current out of  $V_{CC}$  is not limited. Care should be taken to prevent shorting  $V_{CC}$  to Ground.

<sup>\*</sup>The maximum package power dissipation must be observed.

**ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> =  $-40^{\circ}$ C to 125°C, V<sub>SS</sub> = 9.0 to 16 V, V<sub>5REF</sub> I<sub>LOAD</sub> = 2.0 mA, SYNC<sub>OUT</sub> Free Running, unless otherwise specified. For All Specs: UVSD = 6.0 V, OVSD = 0 V, ENABLE = 0 V, I<sub>LIM(1,2)</sub> = 0, V<sub>FB(1,2)</sub> = 3.0 V, R<sub>FADJ</sub> = R<sub>DLYSET</sub> = 27.4 k $\Omega$ .)

| Characteristic                             | Test Conditions                                                                                                       | Min  | Тур  | Max  | Unit |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>SS</sub> Supply Current             |                                                                                                                       |      |      |      |      |

| V <sub>SS</sub> Supply Current             | Measure current into $V_{SS}$ when $V_{5REF} I_{LOAD} = 0$ mA. $9.0 \text{ V} \le V_{SS} \le 13 \text{ V}$ .          | -    | 16   | 23   | mA   |

|                                            | Measure current into V <sub>SS</sub> when  V <sub>5REF</sub> I <sub>LOAD</sub> = 0 mA. 13 V < V <sub>SS</sub> ≤ 16 V. | _    | 16   | 25   | mA   |

|                                            | Measure current into V <sub>SS</sub> when V <sub>5REF</sub> I <sub>LOAD</sub> = 0 mA. 16 V < V <sub>SS</sub> ≤ 20 V.  | -    | 16   | 30   | mA   |

| Low V <sub>CC</sub> Supply Current         |                                                                                                                       |      |      |      |      |

| Low V <sub>CC</sub> Supply Current         | Float $V_{SS}$ . Set $V_{CC}$ = 7.0 V & measure $V_{CC}$ current while $V_{5REF}$ $I_{LOAD}$ = 0 mA.                  | _    | 1.5  | 3.5  | mA   |

| V <sub>SS</sub> to V <sub>CC</sub> Diode   |                                                                                                                       |      |      |      |      |

| Diode ON Voltage                           | Measure V <sub>SS</sub> – V <sub>CC</sub>                                                                             | 0.2  | 0.75 | 1.0  | V    |

| Reference                                  |                                                                                                                       |      |      | .0   |      |

| 5.0 V Internal Voltage Reference           | Measure V <sub>REF</sub> voltage when I <sub>REF</sub> = 0 and I <sub>REF</sub> = 20 mA                               | 4.85 | 5.0  | 5.15 | V    |

| V <sub>REF</sub> OK Threshold              | Adjust V <sub>REF</sub> from 4.8 V-4.0 V<br>until PWM1,2 goes low.                                                    | 4.3  | 4.55 | 4.7  | V    |

| Low V <sub>CC</sub> Lockout                |                                                                                                                       | × 60 |      |      |      |

| V <sub>CC</sub> Turn-on Threshold Voltage  | V <sub>CC</sub> increasing until I <sub>CC</sub> > 3.5 mA<br>V <sub>5REF</sub> I <sub>LOAD</sub> = 0 mA               | 7.0  | 7.25 | 7.5  | V    |

| V <sub>CC</sub> Turn-off Threshold Voltage | V <sub>CC</sub> decreasing until I <sub>CC</sub> < 3.5 mA<br>V <sub>5REF</sub> I <sub>LOAD</sub> = 0 mA               | 6.3  | 6.7  | 7.1  | V    |

| Hysteresis                                 | Turn-on – Turn-off                                                                                                    | 0.40 | 0.55 | 0.70 | V    |

| Clock                                      | 10 11h 0h                                                                                                             |      |      |      |      |

| Operating Frequency1                       | Measure frequency from SYNC <sub>OUT</sub> .                                                                          | 485  | 512  | 540  | kHz  |

| SYNC <sub>IN</sub> Input Impedance         | Measure input impedance.                                                                                              | 7.0  | 15   | -    | kΩ   |

| SYNC <sub>OUT</sub> Output Low Voltage     | $R_{LOAD}$ = 2.0 kΩ to $V_{5REF}$                                                                                     | -    | 1.0  | 1.5  | V    |

| SYNC <sub>OUT</sub> Output High Voltage    | R <sub>LOAD</sub> = 2.0 kΩ to GND                                                                                     | 3.5  | 4.2  | -    | V    |

| SYNC <sub>IN</sub> Detect Frequency        | Verify SYNC <sub>OUT</sub> = SYNC <sub>IN</sub> ,<br>$R_{LOAD}$ = 2.0 k $\Omega$ to GND                               | 425  | -    | 555  | kHz  |

| Max. Low SYNC Rej. Frequency               | Verify SYNC <sub>OUT</sub> = FCLK when $R_{LOAD}$ = 2.0 k $\Omega$ to GND                                             | -    | -    | 340  | kHz  |

| Min. High SYNC Rej. Frequency              | Verify SYNC <sub>OUT</sub> = FCLK when $R_{LOAD}$ = 2.0 k $\Omega$ to GND                                             | 690  | -    | -    | kHz  |

| SYNC <sub>IN</sub> Input Threshold Voltage | Functional Testing Verify FCLK from 1.0 V to 2.8 V                                                                    | 0.9  | 1.85 | 2.9  | V    |

| Main PWM Clock Pulse Width                 | (GBD) - CLPH1 One Shot Pulse Width                                                                                    | 80   | 100  | 120  | ns   |

| Aux PWM Clock Pulse Width                  | (GBD) - CLPH2 One Shot Pulse Width                                                                                    | 80   | 100  | 120  | ns   |

**ELECTRICAL CHARACTERISTICS (continued)** (T<sub>J</sub> = -40°C to 125°C, V<sub>SS</sub> = 9.0 to 16 V, V<sub>5REF</sub> I<sub>LOAD</sub> = 2.0 mA, SYNC<sub>OUT</sub> Free Running, unless otherwise specified. For All Specs: UVSD = 6.0 V, OVSD = 0 V, ENABLE = 0 V, I<sub>LIM(1,2)</sub> = 0, V<sub>FB(1,2)</sub> = 3.0 V, R<sub>FADJ</sub> = R<sub>DLYSET</sub> = 27.4 k $\Omega$ .)

| Characteristic                  | Test Conditions                                                                                          | Min  | Тур   | Max      | Unit |

|---------------------------------|----------------------------------------------------------------------------------------------------------|------|-------|----------|------|

| Bias Supply Error Amplifier     |                                                                                                          |      |       | •        | •    |

| Output Low Voltage              | V <sub>SS</sub> > 12.6 V. Measure OAOUT voltage when sinking 1.0 mA.                                     | _    | 43    | 85       | mV   |

| Output High Voltage             | V <sub>SS</sub> < 11.4 V. Measure OAOUT voltage when sourcing 150 μA.                                    | 4.55 | 4.75  | -        | V    |

| Output High Source Current      | V <sub>SS</sub> < 11.4 V. Measure OAOUT source current when OAOUT = 0.5 V                                | 150  | 225   | 300      | μΑ   |

| Output Low Sink Current         | V <sub>SS</sub> > 12.6 V. Measure OAOUT sink current when OAOUT = 2.5 V.                                 | 3.0  | 20    | 50       | mA   |

| V <sub>SS</sub> Set Point       | Adjust V <sub>SS</sub> until OAOUT goes low.                                                             | 11.6 | 12.25 | 12.8     | V    |

| Large Signal Gain               | (GBD)                                                                                                    | 15   | _     | <u> </u> | V/mV |

| Unity Gain Bandwidth            | (GBD)                                                                                                    | -    | 1.0   | .05      | MHz  |

| Common Mode Input Range         | (GBD)                                                                                                    | 1.0  | - 6   | 2.0      | V    |

| V <sub>SS</sub> Voltage         |                                                                                                          |      |       |          |      |

| V <sub>SS</sub> Reset Voltage   | Toggle ENABLE between GND & $V_{CC}$ , then adjust $V_{SS}$ from 2.0 $V$ –0.8 $V$ until OAOUT goes high. | 1.0  | 1.4   | 1.8      | V    |

| Undervoltage Lockout            | CO                                                                                                       |      |       |          |      |

| UVSD Turn-On Threshold Voltage  | Adjust UVSD from 4.7 V–5.3 V until GATE1,2 goes high.                                                    | 4.8  | 5.0   | 5.1      | V    |

| UVSD Turn-Off Threshold Voltage | Adjust UVSD from 5.1 V-4.3 V until GATE1,2 goes low.                                                     | 4,45 | 4.7   | 4.95     | V    |

| Hysteresis                      | Turn-on – Turn-off                                                                                       | 0.2  | 0.27  | 0.4      | V    |

| UVSD Input Bias Current         | Set UVSD = 0 V. Measure Current out of UVSD lead.                                                        | -    | 0.2   | 0.5      | μΑ   |

| Overvoltage Lockout             | 5 6 1                                                                                                    |      |       |          |      |

| OVSD Threshold Voltage          | Adjust OVSD from 4.7 V–5.3 V until GATE1,2 goes low.                                                     | 4.85 | 5.0   | 5.15     | V    |

| OVSD Input Bias Current         | Set OVSD = 0 V. Measure Current out of OVSD lead.                                                        | -    | 0.2   | 0.5      | μΑ   |

| ENABLE & PROGRAM                | CV OV                                                                                                    |      |       |          |      |

| ENABLE Lead Output Current      | Measure current out of ENABLE when ENABLE = 0 V                                                          | 100  | 266   | 500      | μΑ   |

| PROGRAM Lead Output Current     | Measure current out of PROGRAM when PROGRAM = 0 V                                                        | 20   | 60    | 100      | μΑ   |

| PROGRAM Threshold Voltage       | ENABLE = GND. Adjust PROGRAM from 1.0 V-1.8 V until GATE1,2 goes high.                                   | 1.2  | 1.4   | 1.6      | V    |

| ENABLE Threshold Voltage        | PROGRAM = GND. Adjust ENABLE from 1.0 V-1.8 V until GATE1,2 goes high.                                   | 1.2  | 1.4   | 1.6      | V    |

**ELECTRICAL CHARACTERISTICS (continued)** (T<sub>J</sub> = -40°C to 125°C, V<sub>SS</sub> = 9.0 to 16 V, V<sub>5REF</sub> I<sub>LOAD</sub> = 2.0 mA, SYNC<sub>OUT</sub> Free Running, unless otherwise specified. For All Specs: UVSD = 6.0 V, OVSD = 0 V, ENABLE = 0 V, I<sub>LIM(1,2)</sub> = 0, V<sub>FB(1,2)</sub> = 3.0 V, R<sub>FADJ</sub> = R<sub>DLYSET</sub> = 27.4 k $\Omega$ .)

| Characteristic                                       | Test Conditions                                                                                                                         | Min   | Тур  | Max  | Unit |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| Output Undervoltage Delay                            |                                                                                                                                         |       |      |      |      |

| OUVDELAY Charging Current                            | Set OUVDELAY = 1.0 V, V <sub>FB1</sub> = 4.4 V Measure OUVDELAY I <sub>CHARGE</sub> .                                                   | 7.5   | 10   | 12.5 | μΑ   |

| OUVDELAY Latch-off Voltage                           | Toggle ENABLE between GND & V <sub>CC</sub> , then adjust OUVDELAY from 4.7 V-5.3 V until GATE1,2, goes low.                            | 4.8   | 5.0  | 5.2  | V    |

| OUVDELAY Set Current                                 | OUVDELAY = VOCLO + 50 mV. Measure current into OUVDELAY.                                                                                | -     | 0.5  | 1.0  | mA   |

| V <sub>FB1</sub> Charge Threshold                    | V <sub>SS</sub> = 1.0 V. Toggle ENABLE between GND & V <sub>CC</sub> , adjust V <sub>FB1</sub> from 3.8 V-4.6 V until GATE1,2 goes low. | 4.05  | 4.22 | 4.4  | V    |

| V <sub>FB2</sub> Charge Threshold                    | V <sub>SS</sub> = 1.0 V. Toggle ENABLE between GND & V <sub>CC,</sub> adjust V <sub>FB2</sub> from 3.8 V-4.6 V until GATE1,2 goes low.  | 3.9   | 4.15 | 4.35 | V    |

| Current Limit Circuits                               |                                                                                                                                         |       | .10  | )    | •    |

| I <sub>LIM1</sub> Current Limit Threshold<br>Voltage | Adjust I <sub>LIM1</sub> from 1.0 V-1.3 V<br>until GATE1 goes low.                                                                      | 1.16  | 1.24 | 1.3  | V    |

| I <sub>LIM1</sub> Short Circuit Threshold<br>Voltage | Adjust I <sub>LIM1</sub> from 1.30 V–1.50 V until GATE1 skips 2–cycles with reference to SYNC <sub>OUT</sub> .                          | 1.35  | 1.44 | 1.51 | V    |

| I <sub>LIM1</sub> Input Bias Current                 | Set I <sub>LIM1</sub> = 0 V. Measure current out of I <sub>LIM1</sub> lead.                                                             | 111-0 | 0.5  | 5.0  | μΑ   |

| I <sub>LIM2</sub> Current Limit Threshold<br>Voltage | Adjust I <sub>LIM2</sub> from 1.0 V-1.3 V<br>until GATE2 goes low.                                                                      | 1.16  | 1.24 | 1.3  | V    |

| I <sub>LIM2</sub> Short Circuit Threshold<br>Voltage | Adjust I <sub>LIM2</sub> from 1.30 V-1.50 V until GATE2 skips 2-cycles with reference to SYNC <sub>OUT</sub> .                          | 1.35  | 1.44 | 1.51 | V    |

| I <sub>LIM2</sub> Input Bias Current                 | Set I <sub>LIM2</sub> = 0 V. Measure current out of I <sub>LIM2</sub> lead.                                                             | -     | 0.5  | 5.0  | μΑ   |

| Voltage Feedback Control                             |                                                                                                                                         |       |      |      |      |

| RAMP1 Offset Voltage                                 | V <sub>FB1</sub> = 0 V. Adjust RAMP1 from 0 V-0.3 V until<br>GATE1 goes low. Measure V <sub>RAMP1</sub> .                               | 0.08  | 0.13 | 0.2  | V    |

| RAMP1 Input Bias Current                             | Set RAMP1 = 0 V. Measure Current out of RAMP1 lead.                                                                                     | -     | 0.5  | 5.0  | μΑ   |

| RAMP2 Offset Voltage                                 | V <sub>FB2</sub> = 0 V. Adjust RAMP2 from 0 V-3.0 V until<br>GATE2 goes low. Measure V <sub>RAMP2</sub> .                               | 0.08  | 0.13 | 0.2  | V    |

| RAMP2 Input Bias Current                             | Set RAMP2 = 0 V. Measure Current out of RAMP2 lead.                                                                                     | -     | 0.5  | 5.0  | μΑ   |

| V <sub>FB1</sub> Input Impedance                     | Measure input impedance.                                                                                                                | 60    | 120  | 220  | kΩ   |

| V <sub>FB2</sub> Input Impedance                     | Measure input impedance.                                                                                                                | 60    | 120  | 220  | kΩ   |

**ELECTRICAL CHARACTERISTICS (continued)** (T<sub>J</sub> = -40°C to 125°C, V<sub>SS</sub> = 9.0 to 16 V, V<sub>5REF</sub> I<sub>LOAD</sub> = 2.0 mA, SYNC<sub>OUT</sub> Free Running, unless otherwise specified. For All Specs: UVSD = 6.0 V, OVSD = 0 V, ENABLE = 0 V, I<sub>LIM(1,2)</sub> = 0, V<sub>FB(1,2)</sub> = 3.0 V, R<sub>FADJ</sub> = R<sub>DLYSET</sub> = 27.4 k $\Omega$ .)

| Characteristic                          | Test Conditions                                                              | Min        | Тур  | Max | Unit |

|-----------------------------------------|------------------------------------------------------------------------------|------------|------|-----|------|

| Gate1, 2, 2B, Output Voltages           | V <sub>SS</sub> = 12 V. V <sub>CC</sub> = V <sub>SS</sub> - V <sub>DON</sub> |            |      |     |      |

| GATE1 Low State                         | PROGRAM = 0 V. Measure GATE1 voltage when sinking 1.0 mA.                    | -          | 0.15 | 0.8 | V    |

| GATE2 Low State                         | PROGRAM = 0 V. Measure GATE2 voltage when sinking 1.0 mA.                    | -          | 0.18 | 0.8 | V    |

| GATE2B Low State                        | PROGRAM = 0 V. Measure GATE2B voltage when sinking 1.0 mA.                   | -          | 0.18 | 0.8 | V    |

| GATE2B High State                       | Measure V <sub>CC</sub> – GATE2B voltage when sourcing 1.0 mA.               | _          | 1.65 | 2.0 | V    |

| GATE2 High State                        | Measure V <sub>CC</sub> – GATE2 voltage when sourcing 1.0 mA.                | <u>-</u> / | 1.65 | 2.0 | V    |

| GATE1 High State                        | Measure V <sub>CC</sub> – GATE1 voltage when sourcing 1.0 mA.                | _          | 1.65 | 2.0 | ٧    |

| Propagation Delays                      |                                                                              | •          | 10   |     |      |

| I <sub>LIM1</sub> Delay to Output GATE1 | Measure delay from I <sub>LIM1</sub> going high to GATE1 going low.          | 1          | 80   | 120 | ns   |

| I <sub>LIM2</sub> Delay to Output GATE2 | Measure delay from I <sub>LIM2</sub> going high to GATE2 going low.          | × -cc      | 80   | 100 | ns   |

| RAMP1 Delay to Output GATE1             | Measure delay from RAMP1 going high to GATE1 going low.                      | CALL OF    | 80   | 115 | ns   |

| RAMP2 Delay to Output GATE2             | Measure delay from RAMP2 going high to GATE2 going low.                      | RIF        | 80   | 100 | ns   |

| GATE2, 2B Non-Overlap Delay             | C.VQQ.                                                                       |            | •    |     |      |

| GATE2 Turn-on Delay from<br>GATE2B      | Measure delay from GATE2B going low @ 1.7 V to GATE2 going high @ 1.7 V.     | 20         | 45   | 70  | ns   |

| GATE2B Turn-on Delay from<br>GATE2      | Measure delay from GATE2 going low @ 1.7 V to GATE2B going high @ 1.7 V.     | 20         | 45   | 70  | ns   |

| GATE1, 2, 2B Rise & Fall Times          | V <sub>SS</sub> = 12 V, V <sub>CC</sub> = V <sub>SS</sub> -V <sub>DON</sub>  |            |      |     |      |

| GATE1 Rise Time                         | Measure GATE1 Rise Time from 90% to 10%.  C <sub>LOAD</sub> = 150 pF.        | -          | 50   | 80  | ns   |

| GATE1 Fall Time                         | Measure GATE1 Fall Time from 10% to 90%.  C <sub>LOAD</sub> = 150 pF.        | -          | 30   | 60  | ns   |

| GATE2 Rise Time                         | Measure GATE2 Rise Time from 90% to 10%. C <sub>LOAD</sub> = 50 pF.          | -          | 50   | 80  | ns   |

| GATE2 Fall Time                         | Measure GATE2 Fall Time from 10% to 90%. C <sub>LOAD</sub> = 50 pF.          | -          | 15   | 30  | ns   |

| GATE2B Rise Time                        | Measure GATE2B Rise Time from 90% to 10%.  C <sub>LOAD</sub> = 50 pF.        | -          | 50   | 80  | ns   |

| GATE2B Fall Time                        | Measure GATE2B Rise Time from 10% to 90%.  C <sub>LOAD</sub> = 50 pF.        | -          | 15   | 30  | ns   |

# PACKAGE PIN DESCRIPTION

| PACKAGE PIN # |                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP-24       | PIN SYMBOL        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1             | UVSD              | Undervoltage shutdown lead. Typically this lead is connected through a resistor divider to the main high voltage ( $V_{IN}$ ) line. If the voltage on this lead is less than 5.0 V then a fault is initiated such that GATE1, GATE2 and GATE2B go low.                                                                                                                                                                     |

| 2             | OVSD              | Overvoltage shutdown lead. Typically this lead is connected through a resistor divider to the main high voltage ( $V_{\rm IN}$ ) line. If the voltage on this lead exceeds 5.0 V then a fault is initiated such that GATE1, GATE2 and GATE2B go low.                                                                                                                                                                       |

| 3             | V <sub>5REF</sub> | 5.0 V reference output lead. Capable of 20 mA nominal output. If this lead falls to 4.5 V, a fault is initiated such that GATE1, GATE2 and GATE2B go low.                                                                                                                                                                                                                                                                  |

| 4             | OAM               | Auxiliary error amplifier minus input. This lead is compared to 1.2 V nominal on the auxiliary error amp plus lead and represents the V <sub>SS</sub> voltage divided by ten.                                                                                                                                                                                                                                              |

| 5             | OAOUT             | Auxiliary error amplifier output lead. Source current 300 μA max.                                                                                                                                                                                                                                                                                                                                                          |

| 6             | OUVDELAY          | Output undervoltage timing capacitor lead. If the controlled output voltages of either the main or the auxiliary supply are such that either $V_{FB1}$ or $V_{FB2}$ is greater that 4.1 V nominal, then capacitor from OUVDELAY to ground will begin charging. If the over voltage duration is such that the OUVDELAY voltage exceeds 5.0 V, then a fault will be initiated such that GATE1, GATE2 and GATE2B will go low. |

| 7             | I <sub>LIM1</sub> | Pulse by pulse over current protection lead for the auxiliary PWM. A voltage exceeding 1.2 V nominal on $I_{LIM1}$ will cause GATE1 to go low. A voltage exceeding 1.4 V nominal on $I_{LIM1}$ will cause GATE1 to go low for at least two clock cycles.                                                                                                                                                                   |

| 8             | RAMP1             | Current Ramp Input Lead for the Auxiliary PWM. A voltage which is linear with respect to current in the primary side of the auxiliary transformer is usually represented on this lead. A voltage exceeding $V_{FB1}$ – 0.13 on RAMP1 will cause GATE1 to go low.                                                                                                                                                           |

| 9             | V <sub>FB1</sub>  | Voltage Feedback Lead for the Auxiliary PWM. A voltage which represents the auxiliary power supply output voltage is fed to this lead. A voltage less than RAMP1+0.13 on $V_{FB1}$ will cause GATE1 to go low.                                                                                                                                                                                                             |

| 10            | V <sub>SS</sub>   | $V_{SS}$ power/feedback input lead. See $V_{CC}$ for description of power operation. In addition, this lead is fed to a divide by ten resistor divider and compared to 1.2 V nominal at the positive side of the error amplifier.                                                                                                                                                                                          |

| 11            | V <sub>CC</sub>   | $V_{CC}$ power input lead. This input runs off a Zener referenced supply until $V_{SS} > V_{CC}$ . Then an internal diode which runs between $V_{SS}$ and $V_{CC}$ turns on and all main power is derived from $V_{SS}$ .                                                                                                                                                                                                  |

| 12            | GATE1             | Auxiliary PWM gate drive lead. This output normally drives the FET which drives the auxiliary transformer.                                                                                                                                                                                                                                                                                                                 |

| 13            | GND               | Ground lead.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14            | GATE2             | Synchronous PWM gate drive lead. This output normally drives the FET which drives the main transformer.                                                                                                                                                                                                                                                                                                                    |

| 15            | GATE2B            | Synchronous PWM gate drive lead. This output normally drives the FET for the gate drive transformer used for synchronous rectification.                                                                                                                                                                                                                                                                                    |

| 16            | V <sub>FB2</sub>  | Voltage feedback lead for the synchronous PWM. A voltage which represents the main power supply output voltage is fed to this lead. A voltage less than RAMP2+0.13 on $V_{FB2}$ will cause GATE2 to go low and GATE2B to go high.                                                                                                                                                                                          |

| 17            | RAMP2             | Current ramp input lead for the synchronous PWM. A voltage which is linear with respect to current in the primary side of the main transformer is usually represented on this lead. A voltage exceeding $V_{FB2}$ – 0.13 on RAMP2 will cause GATE2 to go low and GATE2B to go high.                                                                                                                                        |

| 18            | I <sub>LIM2</sub> | Pulse by pulse over current protection lead for the synchronous PWM. A voltage exceeding 1.2V nominal on $I_{LIM2}$ will cause GATE2 to go low and GATE2B to go high. A voltage exceeding 1.4 V nominal on $I_{LIM2}$ will cause GATE2 to go low and GATE2B to go high for at least two clock cycles.                                                                                                                      |

| 19            | DLYSET            | GATE2, GATE2B non–overlap time adjustment lead. A 27 k $\Omega$ resistor from DLYSET to ground sets the non–overlap time to 45 ns nominal.                                                                                                                                                                                                                                                                                 |

| ACKAGE PIN# |                     |                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP-24     | PIN SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                              |

| 20          | FADJ                | Frequency adjustment lead. A 27 $k\Omega$ resistor from FADJ to ground sets the clock frequency to 512 kHz nominal.                                                                                                                                                                                                                   |

| 21          | SYNC <sub>OUT</sub> | Clock output lead. This is a 50% duty cycle, 1.0 V to 5.0 V pulse whose rising edge is in phase with GATE1. This signal can be used to synchronize other power supplies.                                                                                                                                                              |

| 22          | SYNC <sub>IN</sub>  | Clock synchronization lead. The internal clock frequency can be adjusted +10%, -15% by the onset of positive edges of an external clock occurring on the SYNC <sub>IN</sub> lead. If the extern clock frequency is outside the internal clock frequency by +25%, -35% the external clock is ignored and the internal clock free runs. |

| 23          | PROGRAM             | ENABLE programming input. See ENABLE for programming states. PROGRAM has at lea 20 µA min. of available source current.                                                                                                                                                                                                               |

| 24          | ENABLE              | PWM enable input. If PROGRAM is HIGH then a LOW on ENABLE will allow GATE1, GATE2 and GATE2B to switch. If PROGRAM is LOW then a HIGH on ENABLE will allow GATE1, GATE2 and GATE2B to switch. If ENABLE is left floating, it will pull up to a HIGH level. ENABLE has at least 100 $\mu$ A (min) of available source current.         |

|             | PIER                | Chicking of Skinicondition  THIS DEVICE OF THE FOR INFORMATION  REPRESENTATIVE FOR INFORMATION                                                                                                                                                                                                                                        |

#### THEORY OF APPLICATION

#### THEORY OF OPERATION

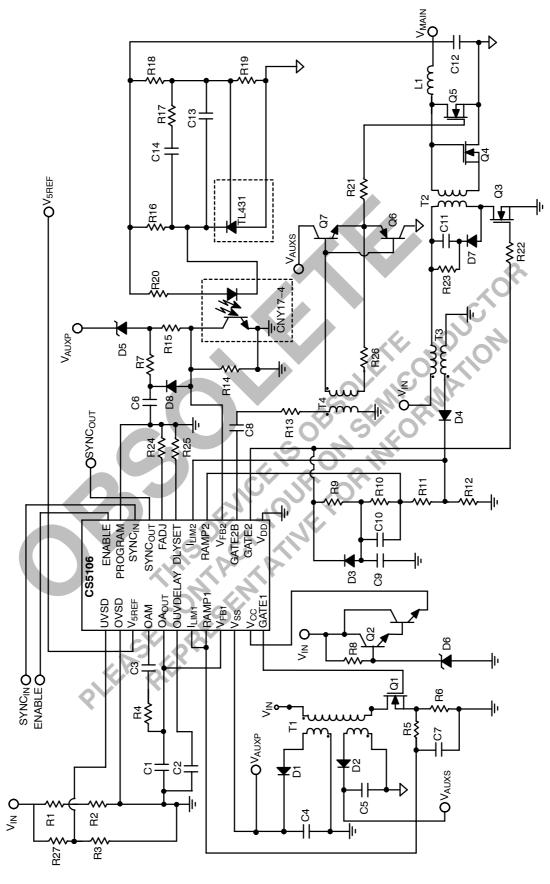

## Powering the IC

The IC has one supply,  $V_{\rm CC}$ , and one Ground lead. If  $V_{\rm SS}$  is used for a bootstrapped supply the diode between  $V_{\rm SS}$  and  $V_{\rm CC}$  is forward biased, and the IC will derive its power from  $V_{\rm SS}$ . The internal logic monitors the supply voltage,  $V_{\rm CC}$ . During abnormal operating conditions, all GATE drivers are held in a low state. The CS5106 requires 1.5 mA nominal of startup current.

#### Startup

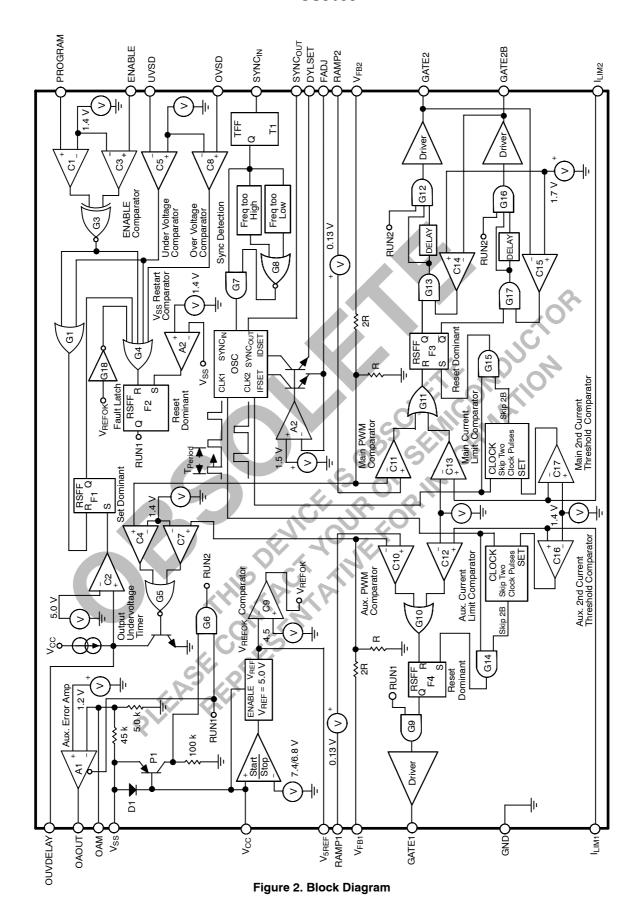

Assume the part is enabled and there are no over voltage or under voltage faults present. Also, assume that all auxiliary and main regulated output voltages start at 0 V. An 8.0 V, Zener referenced supply is typically applied to  $V_{CC}$ . When V<sub>CC</sub> exceeds 7.5 V, the 5.0 V reference is enabled and the OSC begins switching. If the V<sub>5REF</sub> lead is not excessively loaded such that  $V_{5REF}$  < 4.5 V nominal, 'V<sub>REF</sub>OK' goes 'high' and 'RUN1' will go 'high', releasing GATE1 from its low state. After GATE1 is released, it begins switching according to conditions set by the auxiliary control loop and the auxiliary supply, V<sub>SS</sub> begins to rise. When  $V_{SS} > V_{CC} + V(D1)$ , P1 turns on and 'RUN2' goes 'high', releasing GATE2 and GATE2B from their low state. GATE2 and GATE2B begin switching according to conditions set by the main control loop and the main regulated output begins to rise. See startup waveforms in Figure 3.

## **Soft Start**

Soft Start for the auxiliary power supply is accomplished by placing a capacitor between OAOUT and Ground. The error amplifier has 200 µA of nominal of source current and is ideal for setting up a Soft Start condition for the auxiliary regulator. Care should be taken to make sure that the Soft Start timing requirements are not in conflict with any transient load requirements for the auxiliary supply as large capacitors on OAOUT will slow down the loop response. Also, the Soft Start capacitor must be chosen such that during start or restart, both outputs will come into regulation before the OUVDELAY timer trips. Soft Start capacitor C6 through D5 and R7 at start up. After the main supply has come into regulation C6 continues to charge and is disconnected from the feedback loop by D8.

Figure 3. Startup Waveforms

# Voltage and Current Ramp PWM Comparator Inputs (V<sub>FB1,2</sub> and RAMP1,2 leads)

C10 and C11 are the PWM comparators for the auxiliary and main supplies. The feedback voltage ( $V_{FB}$ ) is divided by three and compared with a linear, voltage representation of the current in the primary side of the transformer (RAMP). When the output of the feedback comparator goes 'high', a reset signal is sent to the PWM flip–flop and the GATE driver is driven 'low'. A 130 mV offset on the RAMP leads allows the drivers to go to 0% duty cycle in the presence of light loads.

#### Feedback Voltage for GATE1 Driver (V<sub>FR1</sub>)

Typically the output of the auxiliary error amplifier (A1) is tied to  $V_{FB1}$ . The  $V_{SS}$  output is programmed to 12 V by a 10:1 resistive divider on the negative input of the error amplifier and a fixed 1.2 V reference on the positive input of the error amplifier.

# Pulse by Pulse Over Current Protection and Hiccup Mode (I<sub>LIM1,2</sub> leads)

C12 and C13 are the pulse by pulse current limit comparators for the auxiliary and main supplies. When the current in the primary side of the transformer increases such that the voltage across the current sense resistor exceeds 1.2 V nominal, the output of the current limit comparator goes

'high' and a reset signal is sent to the PWM flip-flop and the GATE driver is driven 'low'.

C16 and C17 are the second threshold, pulse by pulse current limit comparators for the auxiliary and main supplies. If the current in the primary side of the transformer increases so quickly that the current sense voltage is not limited by C12 or C13 and the voltage across the current sense resistor exceeds 1.4 V, the second threshold comparator will trip a delay circuit and force the GATE driver stage to go low and stay low for the next two clock cycles.

#### **Undervoltage and Overvoltage Thresholds**

C5 and C8 are the undervoltage and overvoltage detection comparators. Typically, these inputs are tied across the middle resistor in a three resistor divider with the top resistor to  $V_{IN}$  and bottom resistor to Ground. The under voltage comparator has 200 mV of built in hysteresis with respect to a direct input on the UVSD lead. The under voltage comparator has its positive input referenced to 5.0 V while the over voltage comparator has its negative input referenced to 5.0 V. The output of both comparators are ORed at (G4) with the over current and enable inputs. The output of G4 feeds the input to the fault latch (F2).

#### **PROGRAM and ENABLE Leads**

The PROGRAM lead controls the polarity of the ENABLE lead. If the PROGRAM lead is 'high' or floating, the GATE outputs will go low if the ENABLE input is tied 'high' or floating. If the PROGRAM lead is tied low, the GATE outputs will go low if the ENABLE input is tied 'low'. If the part is then enabled after switching the outputs low, the part will restart according to the procedure outlined in the "Startup" section.

#### **FAULT Logic**

If a  $V_{REF}$ , UVSD or OVSD fault occurs at any time, G4 resets the fault latch (F2). RUN1 goes low and all gate drivers cease switching and return to their 'low' state. When RUN1 goes low, the output of the auxiliary op–amp (A1) discharges the Soft Start capacitor and holds it low while RUN1 is low. If the fault condition is removed before the OUVDELAY timer is tripped, the IC will restart the power supplies when  $V_{SS}$  < 1.4 V. If the OUVDELAY timer trips, the power supply must be restarted as explained in the following section.

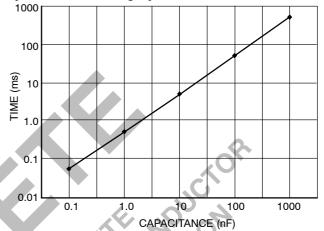

# Output Undervoltage Delay Timer for the Main and Auxiliary Regulated Outputs

C7 and C4 are the output under voltage monitor comparators for the auxiliary and main supplies. If a regulated output drops such that its associated  $V_{FB}$  voltage exceeds 4.1 V, the output undervoltage monitor comparator goes 'high' and the OUVDELAY capacitor begins charging from 0 V. A timing relation is set up by a 10  $\mu A$  nominal current source, the OUVDELAY capacitor and a 5.0 V fault threshold at the input of C2 (see Figure 4). If any regulated output drops and stays low for the entire charge time of the OUVDELAY capacitor, a fault is triggered and all GATE drivers will go into a low state.

Once this fault is triggered, the IC will restart the power supplies only if the OUVDELAY fault is reset and ENABLE or UVSD is toggled while  $V_{SS} < 1.4~V$ . To reset the OUVDELAY fault, both the  $V_{FB}$  inputs must be less than 4.1 V. In the application circuit shown,  $V_{FB1}$  is brought low by OAOUT when RUN1 stops the oscillators.  $V_{FB2}$  is brought low when  $V_{AUXP}$  bleeds down and the  $V_{FB2}$  opto–isolator is no longer powered.

Figure 4. OUVDELAY Time vs. OUVDELAY Capacitance

### **FADJ and DLYSET Leads**

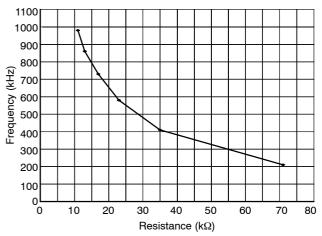

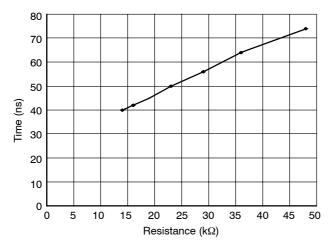

Amplifier A2 and transistor N3 create a current source follower whose output is FADJ. An external resistor from FADJ to ground completes the loop. The voltage across the resistor is set by a buffered, trimmed, precision reference. In this fashion, an accurate current is created which is used to charge and discharge an internal capacitor thereby creating an oscillator with a tight frequency tolerance. For FADJ resistor value selection, see Figure 5. Transistor N2 is in parallel with N3 and is used to created an independent current across the resistor from DLYSET to ground. This current is used to program the GATE non–overlap delay blocks in the main PWM drivers. For DLYSET resistor value selection, see Figure 6.

Figure 5. SYNC<sub>OUT</sub> Frequency vs. FADJ Resistors

Figure 6. GATE Non-Overlap Time vs. DLYSET Resistance

#### Oscillator

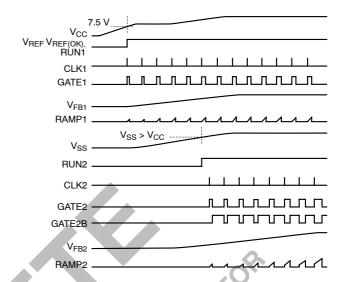

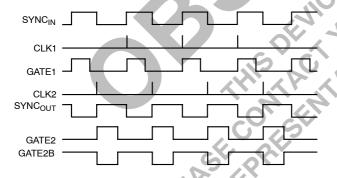

The oscillator generates two clock signals which are 180 degrees out of phase with respect to time. One clock signal feeds the main driver and the other feeds the auxiliary driver. Because the drivers are never turned on at the same time, ground noise and supply noise is minimized. The clock signals are actually 100 ns pulse spikes. These spikes create a narrow driver turn–on window. This narrow window prevents the driver from spurious turn on in the middle of a clock cycle. The oscillator can be synchronized by an external clock (slave) or drive the clocks of other controllers (master). See Figure 7 for the relationship between SYNC, CLK, and GATE waveforms.

Figure 7. SYNC, GATE and CLOCK Waveforms

### SYNC<sub>IN</sub> and SYNC<sub>OUT</sub> Leads

Multiple supplies can be synchronized to one supply by using the SYNC leads. The SYNC $_{\rm IN}$  and SYNC $_{\rm OUT}$  pulses are always 180 degrees out of phase. The SYNC $_{\rm IN}$  input is always in phase with the clock signal for the main driver and the SYNC $_{\rm OUT}$  output is always in phase with the clock signal for the auxiliary driver. If the IC is being used as a slave, the incoming frequency must be within +10%, -20% of the programmed frequency set by its own FADJ resistor. If the frequency on the SYNC $_{\rm IN}$  lead is outside the internal frequency by +25%, -35%, the SYNC $_{\rm IN}$  input will be ignored. If the SYNC signal stops while the power supplies are in synchronized operation, the synchronized supplies

will stop and restart free running. If the SYNC<sub>IN</sub> signal drifts out of frequency specification while the power supplies are in synchronized operation, the synchronized supplies will begin to free run without restarting.

#### Slope Compensation

DC-DC converters with current mode control require slope compensation to avoid instability at duty cycles greater than 50%. A slope is added to the current sense waveform (or subtracted from the voltage waveform) that is equal to a percentage (75% typical) of the down slope of the inductor current. In the application diagram shown, the bootstrap (flyback) transformer inductance can be chosen so that the duty cycle never exceeds 50% and therefore does not require slope compensation. The buck indicator in the forward converter would typically be chosen to work in continuous conduction mode with a maximum duty cycle of 50-60% and would require slope compensation. Slope compensation is accomplished as follows: R9 and C9 form a ramp waveform rising each time GATE 2 turns on. C9 is discharged through D3 to the same level each cycle regardless of duty cycle. R10 and R11 are chosen to control the amount of slope compensation. C10 provides filtering for noise and turn-on spikes. To calculate the required slope compensation, calculate the buck indicator down current and the corresponding voltage slope at the current sense resistor - R12.

The buck inductor down slope is:

Inductor\_Slope =

$$\frac{V_{OUT} + V_{Q5}}{L_{1}(\mu H)} \left(\frac{A}{\mu s}\right)$$

The equivalent down slope at the current sense resistor for this application circuit is:

Slope @ R12 = Inductor\_Slope

$$\times \frac{NST2}{NPT2} \times \frac{NPT3}{NST3} \times R12 \left(\frac{V}{\mu s}\right)$$

After choosing R9 and C9 to generate a ramp with a time constant of about 5 times the oscillator period, R10 and R11 can be chosen for the voltage at RAMP2 to be 1.75 of the voltage across R12.

#### Synchronous Rectification

Synchronous rectification was chosen to reduce losses in the forward converter. Improvements in efficiency will be most significant in low voltage, medium and high current converters where improvement in conduction loss offsets any added losses for gate drive.

In the application circuit Q4 is turned on and off by the forward transformer. Q5 is turned on and off through pulse transformer T4 and the gate driver formed by Q6 and Q7. Because Q4 and Q5 are driven through different types of components, differences in propagation delay must be considered. The DLYSET resistor should be chosen to avoid shoot–through or excessive off time.

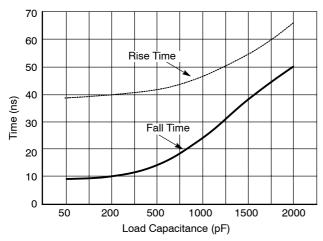

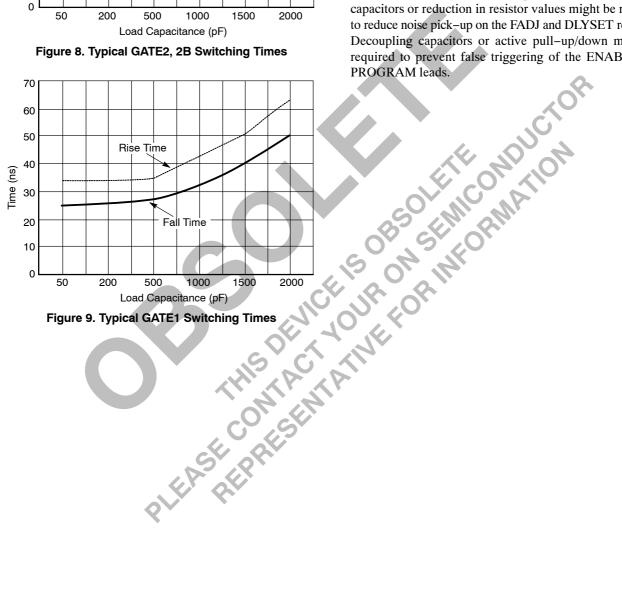

#### **Gate Drive Capability**

All GATE drive outputs have nominal peak currents of 0.5A. See Figures 8 and 9 for typical rise and fall times.

Figure 8. Typical GATE2, 2B Switching Times

Figure 9. Typical GATE1 Switching Times

#### **Design Considerations**

The circuit board should utilize high frequency layout techniques to avoid pulse width jitter and false triggering of high impedance inputs. Ground plane(s) should be employed. Signal grounds and power grounds should be run separately. Portions of the circuit with high slew rates or current pulses should be segregated from sensitive areas. Shields and decoupling capacitors should be used as required.

Special care should be taken to prevent coupling between the SYNC leads and the surrounding leads. Depending on the circuit board layout and component values, decoupling capacitors or reduction in resistor values might be required to reduce noise pick-up on the FADJ and DLYSET resistors. Decoupling capacitors or active pull-up/down might be required to prevent false triggering of the ENABLE and

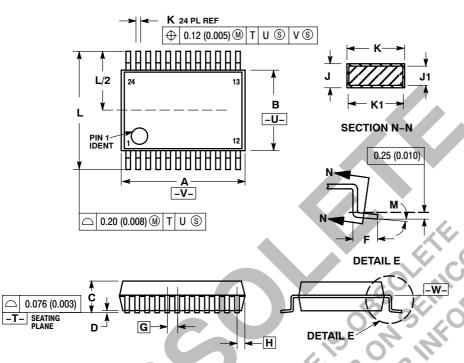

#### PACKAGE DIMENSIONS

SSOP-24 **SW SUFFIX** CASE 940D-03 **ISSUE D**

#### NOTES

- DIMENSIONING AND TOLERANCING PER ANSI 1. DIMEINO. Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

- B. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

- I. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

- DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION/INTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF K DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR INTRUSION SHALL NOT REDUCE DIMENSION K BY MORE THAN 0.07 (0.002) AT LEAST MATERIAL CONDITION.

TERMINAL NUMBERS ARE SHOWN FOR

- REFERENCE ONLY.

7. DIMENSION A AND B ARE TO BE

DETERMINED AT DATUM PLANE -W-.

|     |        | _      |           |       |

|-----|--------|--------|-----------|-------|

|     | MILLIN | IETERS | INC       | HES   |

| DIM | MIN    | MAX    | MIN       | MAX   |

| Α   | 8.07   | 8.33   | 0.317     | 0.328 |

| В   | 5.20   | 5.38   | 0.205     | 0.212 |

| C   | 1.73   | 1.99   | 0.068     | 0.078 |

| D   | 0.05   | 0.21   | 0.002     | 0.008 |

| F ( | 0.63   | 0.95   | 0.024     | 0.037 |

| G   | 0.65   | BSC    | 0.026 BSC |       |

| H   | 0.44   | 0.60   | 0.017     | 0.024 |

| J   | 0.09   | 0.20   | 0.003     | 0.008 |

| J1  | 0.09   | 0.16   | 0.003     | 0.006 |

| K   | 0.25   | 0.38   | 0.010     | 0.015 |

| K1  | 0.25   | 0.33   | 0.010     | 0.013 |

| L   | 7.65   | 7.90   | 0.301     | 0.311 |

| M   | 0 °    | 8 °    | 0 °       | 8 °   |

#### **PACKAGE THERMAL DATA**

| Parameter        | 1       | SSOP-24 | Unit |

|------------------|---------|---------|------|

| R <sub>eJC</sub> | Typical | 23      | °C/W |

| $R_{\Theta JA}$  | Typical | 117     | °C/W |

| ERSE COLES       |         |         |      |

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) . Solitude services are inject to make triangles without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative